## Applikation JTAG/Boundary Scan

BSDL Verification • Design Validation • Hardware Debugging • Component Programming • Structural Test • Functional Test • Emulation Test • Mixed Signal Test • Optoelectric Test

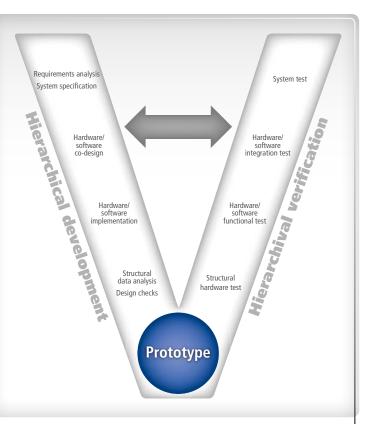

### The V-Model Leads the Way

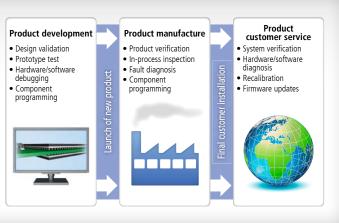

Each product life cycle is defined by the following stages:

- hierarchical prototype development and validation

- pilot run production and testing

- field maintenance and repair of serial products.

All of these stages are based on their own processes and require **target-oriented applications**. In essence, the foundation for high product quality is already laid in the development labs.

The **"V-model**" plays a significant part in controlling increasingly complex designs. It defines adequate partial verifications for each hierarchical

The V-model harmonises development and validation -

Overview of a **product life cycle** —

development stage by means of **specific test procedures**. These verifications include:

- structural tests (structural validation of the hardware)

- functional tests (functional validation of the modules)

- integration tests (interface validation of the modules)

- system tests (functional validation of the prototype)

In addition, parametric tests with firmware or hardware specifically programmed in part to optimise the prototype are typically performed in the course of these validations. This leads to a series of **other procedures** such as:

- performance tests (optimisation of the system performance)

- stress tests (optimisation of the system stability)

- reconfigurations (flash/PLD/MCU programming)

Even though the final objectives in the **individual stages of the product life cycle** differ, they use a number of essentially **identical** test and programming **applications**.

| Feature                  | Laboratory                                                                                                                                                             | Production                                                                                                                                                                          | Field                                                                                                                                                                                             |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Objective                | marketable<br>prototype                                                                                                                                                | salable<br>batch product                                                                                                                                                            | avalable<br>system                                                                                                                                                                                |  |

| Test focus               | design error                                                                                                                                                           | • production error                                                                                                                                                                  | operating error                                                                                                                                                                                   |  |

| Optimisation<br>criteria | <ul> <li>development period</li> <li>validation quality</li> <li>time-to-market</li> <li>fast prototyping</li> <li>reliability</li> <li>testability</li> </ul>         | <ul> <li>fault coverage</li> <li>test throughput</li> <li>diagnosis quality</li> <li>test costs</li> <li>yield</li> <li>repair costs</li> </ul>                                     | <ul> <li>diagnosis costs</li> <li>repair time</li> <li>repair costs</li> <li>maintenance costs</li> <li>calibration costs</li> <li>MTTF/MTBF</li> </ul>                                           |  |

| Test processes           | <ul> <li>structural test<sup>1</sup></li> <li>functional test</li> <li>system test</li> <li>integration test</li> <li>performance test</li> <li>stress test</li> </ul> | <ul> <li>structural test<sup>1</sup></li> <li>functional test</li> <li>system test</li> <li>diagnosis test<sup>2</sup></li> <li>self-test<sup>2</sup></li> <li>HASS/HALT</li> </ul> | <ul> <li>structural test<sup>1</sup></li> <li>functional test</li> <li>system test</li> <li>diagnosis test<sup>2</sup></li> <li>self-test<sup>2</sup></li> <li>remote test<sup>2</sup></li> </ul> |  |

| Debugging<br>processes   | <ul><li>firmware</li><li>hardware</li></ul>                                                                                                                            | • hardware                                                                                                                                                                          | <ul> <li>hardware</li> <li>software<sup>2</sup></li> </ul>                                                                                                                                        |  |

| Programming<br>processes | PLD/FPGA     flash memory     micro controller                                                                                                                         | <ul> <li>PLD/FPGA</li> <li>flash memory</li> <li>micro controller</li> </ul>                                                                                                        | <ul> <li>PLD/FPGA<sup>2</sup></li> <li>flash memory<sup>2</sup></li> <li>micro controller<sup>2</sup></li> </ul>                                                                                  |  |

<sup>1</sup> via JTAG/Boundary Scan <sup>2</sup> requires Embedded System Access (ESA)

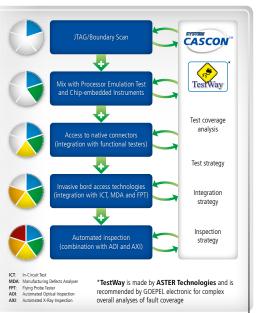

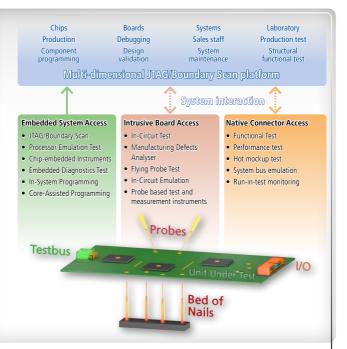

Access to the unit under test (UUT) in order to execute the desired application is a key issue in the case of all above mentioned processes. Using the Embedded System Access (ESA) offers the unique opportunity to use standardised multi-dimensional platforms for JTAG/ Boundary Scan based instrumentation through all product life cycle stages, while continuing to use existing applications.

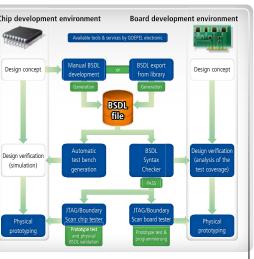

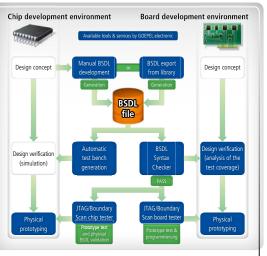

BSDL: connecting element between design and test -

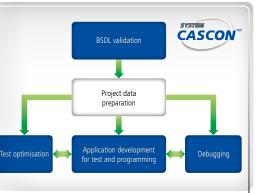

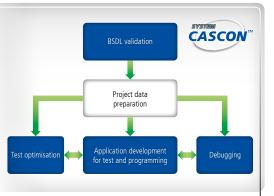

Workflow including debugging and test optimisation -

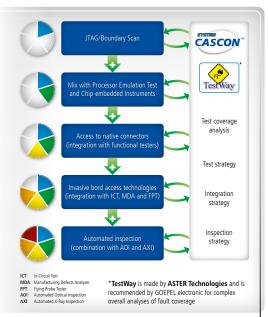

Gradual optimisation of fault coverage -

#### **Keeping Track of the Entire Workflow**

**In addition to** the **core process** for testing and programming, successful project development also requires a number of **supplementary processes** such as:

- BSDL validation

- (BSDL: Boundary Scan Description Language)

- Test program debugging

- Hardware debugging

- Optimisation of testability

- Optimisation of fault coverage

For these processes, too, we offer fully integrated support as part of the available hardware and software platforms, thus ensuring that the **entire workflow** can be covered **in a single system environment**.

| Objectiv              | /e                                                                                                                                                                                                                                                                                                                                 | Software/hardware                                                                                                                                                                                                                                                                   |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BSDL<br>validation    | <ul> <li>Syntax check</li> <li>Semantics check</li> <li>Techn bench generation for simulations</li> <li>Physical verification of the BSDL file against the silicon</li> </ul>                                                                                                                                                      | <ul> <li>TAP Checker</li> <li>Syntax &amp; Semantic Checker</li> <li>ATPG/PFD Infrastructure</li> <li>Device Checker Hardware</li> </ul>                                                                                                                                            |  |  |

| Debugging             | <ul> <li>Test program debugging</li> <li>Pin toggling</li> <li>Scan cell toggling</li> <li>Data register watching</li> <li>Data register loading</li> <li>Waveform analysis</li> <li>Network analysis</li> <li>Instructions change</li> <li>Circuit verification</li> <li>Fault isolation</li> <li>Pin status detection</li> </ul> | <ul> <li>ScanAssist Interactive Pin-Toggler</li> <li>ScanAssist Multi Mode Debugger</li> <li>ScanVision Schematic</li> <li>ScanVision Layout</li> <li>ScanVision Virtual Schematic</li> <li>Advanced Vector Browser</li> <li>PicoTAP, SCANBOOSTER or SCANFLEX Controller</li> </ul> |  |  |

| Test<br>optimisations | <ul> <li>Testability reviews</li> <li>Optimisation of test coverage</li> <li>Maximisation of throughput</li> <li>Definition of the test strategy</li> <li>Qualification of the integration strategy</li> </ul>                                                                                                                     | <ul> <li>Design and Testability Explorer</li> <li>Test Coverage Analyser</li> <li>ScanVision Schematic</li> <li>ScanVision Layout</li> <li>ScanVision Virtual Schematic</li> </ul>                                                                                                  |  |  |

**All processes** are included in the principle of **graphic project development** on which the SYSTEM CASCON is based.

This is made possible by extremely powerful **visualisation tools**, such as **Mission Assist**<sup>™</sup> oder **ScanVision**<sup>™</sup>, which are fully integrated into the software platform. In addition, we offer a broad range of **ATE integration packages** and **automated inspection systems** aimed specifically at test optimisation.

|     | GOEPEL electronic GmbH    | Authorised Distributor: |

|-----|---------------------------|-------------------------|

|     | Goeschwitzer Straße 58/60 |                         |

| ••• | 07745 Jena / Germany      |                         |

|     | Phone: +49(0)-3641-6896-0 |                         |

|     | Fax: +49(0)-3641-6896-944 |                         |

|     | E-Mail: sales@goepel.com  |                         |

|     | Internet: www.goepel.com  |                         |

|     |                           |                         |

BST-AF/E/2012-04

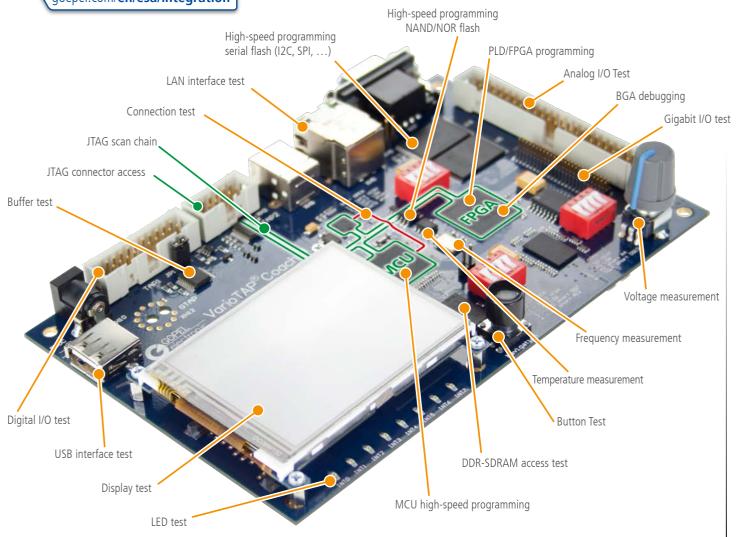

# **Overview: Functional/Emulation Tests, Programming**

|                                          | Test coverage                                                                                                                                                               | С                                                     |         | Controller  |          |                                                                                                                      |                                                                                                   |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------|-------------|----------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| Functional/<br>emulation tests           |                                                                                                                                                                             | Speed <sup>2</sup>                                    | PicoTAP | SCANBOOSTER | SCANFLEX | Required I/O modules                                                                                                 | Required software tools                                                                           |

| Internal chip test                       | <ul> <li>Connections to core logic</li> <li>Core functions</li> </ul>                                                                                                       | • static                                              | •       | •           | •        |                                                                                                                      | • SVF Compiler                                                                                    |

| Cluster test                             | <ul> <li>Connections to the cluster</li> <li>Cluster functions</li> <li>Connections within the cluster</li> </ul>                                                           | • static                                              | •       | •           | •        |                                                                                                                      | ATPG Clusters (Waveform)     ATPG/PFD Clusters (Truth Table)                                      |

| Unit<br>Under<br>Test<br>Board I/O test  | Connectors     Peripheral I/Os     Board functions     Connections within boards     Simulated functions by means of DTIF*     (Digital Test interchange Format, IEEE 1445) | static     at-speed*     *PXI or SCANFLEX I/O modules | •       | •           | •        | CION Modules     PXI I/O modules     SCANFLEX I/O modules                                                            | ATPG/PFD IEEE 1445 (DTIF)     ATPG/PFD Clusters (Truth Table)     ATPG Clusters (Waveform)        |

| Core-assisted RAM access test            | <ul> <li>SRAM connections</li> <li>DRAM connections</li> <li>DDR-SDRAM connections</li> <li>Inline buffer</li> </ul>                                                        | • at-speed                                            |         |             | •        |                                                                                                                      | AVTG <sup>1</sup> Dynamic Memory Access     PFD Memory Access     VarioTAP IP for micro processor |

| Levice Core-assisted system bus test     | <ul> <li>Bus connections</li> <li>Write and read functions</li> <li>Bus device functions</li> <li>Board and system functions</li> <li>Switches, LEDs, displays</li> </ul>   | • at-speed                                            |         |             | •        |                                                                                                                      | AVTG Bus Devices     PFD Clusters (Truth Table)     VarioTAP IP for micro processor               |

| LIVO<br>module<br>Core-assisted I/O test | <ul> <li>Analog and digital I/Os</li> <li>Communication bus interface</li> <li>Actuators, sensors</li> <li>System bus interface</li> </ul>                                  | <ul><li>at-speed</li><li>real time</li></ul>          |         |             | •        | CION Modules     PXI I/O modules     SCANFLEX I/O modules     including Bus Acces Cables     ICT'/FPT'/FCT' channels | AVTG Bus Devices     Basic VarioTAP Test Generation     VarioTAP IP for micro processor           |

|                                                                                           |                                                                                                                                                                              |                                                                                        | Controller                          |                                                                                            |                                                                                                                        |

|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| Programming of components                                                                 | Test coverage                                                                                                                                                                | Speed <sup>2</sup>                                                                     | PicoTAP<br>SCANBOOSTER<br>SCANFLEX  | Required I/O modules                                                                       | Required software tools                                                                                                |

| PLD/FPGA programming                                                                      | <ul> <li>Programmable Logic Device (PLDs)</li> <li>Field Programmable Gate Arrays (FPGAs)</li> </ul>                                                                         | • Depends on the controller                                                            | * * *                               |                                                                                            | • PLD Program Generators                                                                                               |

| Boundary Scan flash programming                                                           | Parallel NAND flash memory     Parallel NOR flash memory     Serial flash memory (I <sup>2</sup> C, SPI)     Electronic multimedia cards     Phase-change memory             | Low to medium     Recommended: high-speed     programming via VarioTAP or     ChipVORX | *suitable for<br>small data volumes | _                                                                                          | • Automated Flash ISP (AFPG)                                                                                           |

|                                                                                           | • On-chip flash of micro controllers (MCU)                                                                                                                                   | High-speed up to<br>turbo-speed*     */if flash image transfer via LAN                 | •                                   | SCANFLEX I/O modules<br>including Bus Acces Cables     Option for                          | Automated VarioTAP Flash ISP<br>(AFPG)     VarioTAP IP for micro processor     CASCON <sup>®</sup> CASCON <sup>®</sup> |

| Micro controller programming                                                              | Parallel NAND flash memory     Parallel NOR flash memory     Serial flash memory (I <sup>2</sup> C, SPI)     Embedded multimedia card (eMMC)     Phase change memory         | is availabe     High-speed up to     turbo-speed*     *if flash image transfer via LAN | •                                   | flash image transfer via LAN   SCANFLEX I/O modules including Bus Acces Cables  Option for | Automated VarioTAP Flash ISP<br>(AFPG)     ChipVORX IP     CASCON"                                                     |

| Core-assisted flash programming                                                           | Phase-change memory     Parallel NAND flash memory     Parallel NOR flash memory     Serial flash memory (I <sup>2</sup> C, SPI)     FPGA boot flash     Phase-change memory | • High-speed up to<br>turbo-speed*                                                     | •                                   | flash image transfer via LAN                                                               | Automated Flash ISP (AFPG)     ChipVORX IP                                                                             |

| Boundary Scan methods         Core-assisted Programming         FPGA-assisted Programming |                                                                                                                                                                              |                                                                                        |                                     |                                                                                            |                                                                                                                        |

# Applications Based on Embedded System Access (ESA)

Correlation between application, instrumentation and access -

#### **Classification of Target Applications**

**Each application** pursues certain **basic objectives**, such as testing, programming, debugging or validation, and is defined by certain very specific characteristics, such as execution speed, execution environment or interaction with other instruments. In this context, the **following application types** are especially important for **Embedded System Access (ESA)**.

| Application type   | Key application contents                                                                         |  |  |

|--------------------|--------------------------------------------------------------------------------------------------|--|--|

| Structural test    | Checking the proper connection between the various circuitry elements                            |  |  |

| Functional test    | Checking the proper functioning of ICs, clusters, boards, interfaces and systems                 |  |  |

| Emulation test     | Test conducted by the micro processor through emulation<br>(special instance of functional test) |  |  |

| At-speed test      | Execution: structural, functional or emulation test at higher speed                              |  |  |

| Real time test     | Execution: structural, functional or emulation test at nominal speed                             |  |  |

| Analog measurement | Measurement of voltage, frequency, temperature, waveform                                         |  |  |

| Debugging          | Interactive test of individual registers, pins, connections or logic functions                   |  |  |

| Programming        | Programming of non-volatile memory (flash, micro controller, PLD)                                |  |  |

Our multi-dimensional JTAG/Boundary Scan platform **supports** not only **all** of the above mentioned **applications**, but also offers the option to interactively combine other access methods through open system integration. In this way, we are able to provide a flexible and **universally deployable solution**.

Practical examples of applications based on Embedded System Access technologies -

BSDL: connecting element between design and test

Workflow including debugging and test optimisation ·

Gradual optimisation of fault coverage

### **Keeping Track of the Entire Workflow**

In addition to the core process for testing and programming, successful project development also requires a number of **supplementary processes** such as:

- BSDL validation

- (BSDL: Boundary Scan Description Language)

- Test program debugging

- Hardware debugging

- Optimisation of testability •

- Optimisation of fault coverage •

For these processes, too, we offer fully integrated support as part of the available hardware and software platforms, thus ensuring that the entire workflow can be covered in a single system environment.

| Objective             |                                                                                                                                                                                                                                                                                                                                    | Software/hardware                                                                                                                                                                                                                                                                   |  |  |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BSDL<br>validation    | <ul> <li>Syntax check</li> <li>Semantics check</li> <li>Techn bench generation for simulations</li> <li>Physical verification of the BSDL file against the silicon</li> </ul>                                                                                                                                                      | <ul> <li>TAP Checker</li> <li>Syntax &amp; Semantic Checker</li> <li>ATPG/PFD Infrastructure</li> <li>Device Checker Hardware</li> </ul>                                                                                                                                            |  |  |

| Debugging             | <ul> <li>Test program debugging</li> <li>Pin toggling</li> <li>Scan cell toggling</li> <li>Data register watching</li> <li>Data register loading</li> <li>Waveform analysis</li> <li>Network analysis</li> <li>Instructions change</li> <li>Circuit verification</li> <li>Fault isolation</li> <li>Pin status detection</li> </ul> | <ul> <li>ScanAssist Interactive Pin-Toggler</li> <li>ScanAssist Multi Mode Debugger</li> <li>ScanVision Schematic</li> <li>ScanVision Layout</li> <li>ScanVision Virtual Schematic</li> <li>Advanced Vector Browser</li> <li>PicoTAP, SCANBOOSTER or SCANFLEX Controller</li> </ul> |  |  |

| Test<br>optimisations | <ul> <li>Testability reviews</li> <li>Optimisation of test coverage</li> <li>Maximisation of throughput</li> <li>Definition of the test strategy</li> <li>Qualification of the integration strategy</li> </ul>                                                                                                                     | <ul> <li>Design and Testability Explorer</li> <li>Test Coverage Analyser</li> <li>ScanVision Schematic</li> <li>ScanVision Layout</li> <li>ScanVision Virtual Schematic</li> </ul>                                                                                                  |  |  |

All processes are included in the principle of graphic project development on which the SYSTEM CASCON is based.

This is made possible by extremely powerful visualisation tools, such as Mission Assist<sup>™</sup> oder ScanVision<sup>™</sup>, which are fully integrated into the software platform. In addition, we offer a broad range of ATE integration packages and automated inspection systems aimed specifically at test optimisation.

|     |                           | J                       |

|-----|---------------------------|-------------------------|

|     | Internet: www.goepel.com  |                         |

|     | E-Mail: sales@goepel.com  |                         |

|     | Fax: +49(0)-3641-6896-944 |                         |

|     | Phone: +49(0)-3641-6896-0 |                         |

| ••• | 07745 Jena / Germany      |                         |

|     | Goeschwitzer Straße 58/60 |                         |

|     | GOEPEL electronic GmbH    | Authorised Distributor: |

|     |                           |                         |